Udvikling: 1989-2000

I 1989 mente HP, at RISC-arkitekturer (RISC) med reduceret instruktionssæt (Reduced InstructionSet Computing) var fastlåst på én instruktion pr. cyklus. HP's forskere forsøgte at skabe en ny type processorarkitektur, senere kaldet Explicitly Parallel Instruction Computing (EPIC), som gør det muligt for processoren at bruge mange instruktioner i hver clockcyklus. EPIC anvender en form for VLIW-arkitektur (Very Long Instruction Word), hvor 1 instruktionsord indeholder mange instruktioner. Med EPIC kontrollerer compileren, hvilke instruktioner der kan bruges samtidig, så processoren kan køre instruktionerne uden at have brug for komplicerede metoder til at se, hvilke instruktioner der kan bruges samtidig. Målet med denne idé er at gøre det muligt at foretage en bedre inspektion af koden på kompileringstidspunktet for at kontrollere, om der er yderligere muligheder for flere udførelser på én gang, og at forenkle processordesignet og spare elektricitet ved at fjerne behovet for runtime-planlægningsinstruktioner.

HP mente, at det ikke var godt for individuelle virksomhedssystemvirksomheder som HP at lave proprietære processorer, så HP samarbejdede med Intel i 1994 om at skabe IA-64-arkitekturen, der er udviklet på grundlag af EPIC's idéer. Intel ønskede at gøre en stor indsats for at skabe IA-64 i forventning om, at den resulterende processor ville blive anvendt af de fleste virksomhedssystemer. HP og Intel gjorde en stor konstruktionsindsats for at lave det første Itanium-produkt, Merced, i 1998.

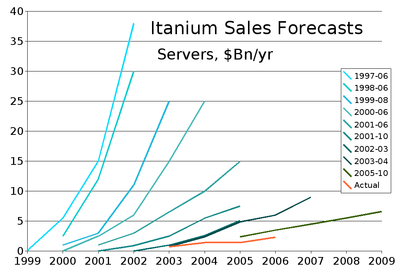

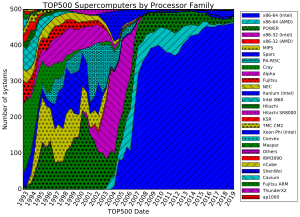

Under oprettelsen troede Intel, HP og andre brancheanalytikere, at IA-64 ville blive meget populær i servere, arbejdsstationer og stationære computere og en dag erstatte RISC- og CISC-arkitekturer (Complex Instruction Set Computing) i multifunktionelle applikationer. Compaq og Silicon Graphics stoppede arbejdet på deres Alpha- og MIPS-arkitekturer for at gå over til Itanium-arkitekturen.

Mange grupper skabte operativsystemer til Itanium, herunder Microsoft Windows, OpenVMS, Linux og UNIX-typer som HP-UX, Solaris, Tru64 UNIX og Monterey/64 (de tre sidste blev aldrig færdiggjort med at køre på Itanium). I 1997 fandt mange ud af, at Itanium-arkitekturen og compileren var vanskeligere at bruge, end de havde troet. Teknologiske problemer som f.eks. det meget høje transistortal, der var nødvendigt for de store instruktionsord og de store caches.[] Der var også problemer med projektet, da de to dele af holdet anvendte forskellige metoder og havde lidt forskellige prioriteringer. []Da Merced var den første EPIC-processor, var der flere problemer med oprettelsen af den, end holdet havde regnet med. Desuden kræver EPIC-konceptet forskellige compiler-færdigheder, som aldrig var blevet skabt før, så der var behov for mere forskning. []

Intel annoncerede navnet på processoren, Itanium, den 4. oktober 1999. I løbet af få timer var navnet Itanic blevet brugt som en joke (en henvisning til Titanic, det "usynkelige" skib, der sank i 1912 ("Itanium + Titanic = Itanic")). "Itanic" er også blevet brugt af The Register og andre til at sige, at investeringen på flere milliarder dollars i Itanium og den tidlige efterspørgsel efter Itanium ikke ville betyde noget, fordi de troede, at Itanium ville gå ned.

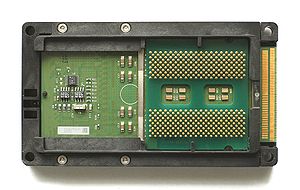

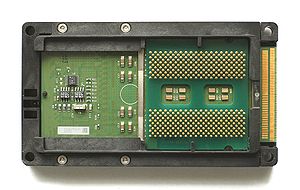

Itanium (Merced): 2001

| Itanium (Merced) |

|

|

| Produceret | Fra juni 2001 til juni 2002 |

| Fælles producent(er) | |

| Max. CPU-ur hastighed | 733 MHz til 800 MHz |

| FSB-hastigheder | 266 MT/s |

| Instruktionssæt | Itanium |

| Antal kerner | 1 |

| L2-cache | 96 KB |

| L3-cache | 2 eller 4 MB |

| Stikkontakt(er) | |

| Kernebetegnelse(r) | |

Da Itanium blev frigivet i juni 2001, var dens ydeevne ikke bedre end konkurrerende RISC- og CISC-processorer. Itanium konkurrerede med systemer med lav effekt (primært 4-CPU'er og små systemer) med servere baseret på x86-processorer og med høj effekt, f.eks. med IBM's POWER-arkitektur og Sun Microsystems' SPARC-arkitektur. Intel ændrede Itanium til at arbejde med højtydende virksomheder og HPC-computere og forsøgte at kopiere x86's succesrige marked (dvs. 1 arkitektur, mange systemleverandører). Succesen for den første processorversion var kun med at erstatte PA-RISC i HP-systemer, Alpha i Compaq-systemer og MIPS i SGI-systemer, men IBM lavede også en supercomputer baseret på denne arkitektur. POWER og SPARC var stærke, og x86-arkitekturen voksede mere ind på virksomhedsområdet på grund af den lettere skalering og den meget store installationsbase.

Der blev kun solgt nogle få tusinde systemer med den første Itanium-processor, Merced, på grund af dårligere ydeevne, høje omkostninger og mindre Itanium-udviklet software. Intel kunne se, at Itanium krævede mere native software for at fungere godt, så Intel lavede tusindvis af systemer til uafhængige softwareleverandører for at hjælpe dem med at lave Itanium-software. HP og Intel bragte den anden Itanium-processor, Itanium 2, på markedet et år senere.

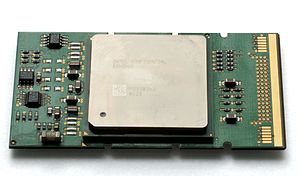

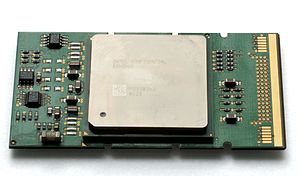

Itanium 2: 2002-2010

| Itanium 2 (McKinley) |

|

|

| Produceret | Fra 2002 til 2010 |

| Designet af | Intel |

| Fælles producent(er) | |

| Max. CPU-ur hastighed | 900 MHz til 2,53 GHz |

| Instruktionssæt | Itanium |

| Antal kerner | 1, 2, 4 eller 8 |

| L2-cache | 256 KB på Itanium2

256 KB (D) + 1 MB(I) eller 512 KB (I) på Itanium2 9x00-serien) |

| L3-cache | 1.5-32 MB |

| Stikkontakt(er) | - PAC611

- FC-LGA6 (LGA1248) (Itanium 9300-serien)

|

| Kernebetegnelse(r) | - McKinley

- Madison

- Hondo

- Deerfield

- Montecito

- Montvale

- Tukwila

- Poulson

|

Itanium 2-processoren blev lanceret i 2002 til virksomhedsservere og ikke til alle højtydende computere. Den første version af Itanium 2, med kodenavnet McKinley, blev udviklet af HP og Intel. Den løste mange af problemerne i den 1. Itanium-processor, som hovedsagelig skyldtes et dårligt hukommelsessubsystem. McKinley havde 221 millioner transistorer (25 millioner af dem var til logik), og var 19,5 mm x 21,6 mm (421 mm 2) og blev skabt med en 180 nm designproces og en CMOS-proces med 6 lag aluminium.

I 2003 lancerede AMD Opteron, som implementerede den første x86-64-arkitektur (dengang kaldet AMD64). Opteron blev en meget større succes, fordi det var en nem opgradering fra x86. Intel implementerede x86-64 i sine Xeon-processorer i 2004.

Intel frigav en ny Itanium 2-processor med kodenavnet Madison i 2003. Madison anvendte en 130 nm-proces og var grundlaget for alle nye Itanium-processorer indtil juni 2006.

I marts 2005 meddelte Intel, at de arbejdede på en ny Itanium-processor med kodenavnet Tukwila, som skulle udgives i 2007. Tukwila ville have 4 processorkerner og ville erstatte Itanium-bussen med en ny Common System Interface, som også ville blive brugt af en ny Xeon-processor. Senere samme år ændrede Intel Tukwila's udgivelsesdato til slutningen af 2008.

I november 2005 arbejdede de største Itanium-serverproducenter sammen med Intel og mange softwareleverandører om at oprette Itanium Solutions Alliance for at fremme arkitekturen og fremskynde tilpasningen af software. Alliancen siger, at dens medlemmer vil investere 10 mia. dollars i Itanium-løsninger inden udgangen af dette årti.

I 2006 leverede Intel Montecito (markedsført som Itanium 2 9000-serien), en 2-kerneprocessor med ca. 2 gange større ydeevne og 20 % mindre energiforbrug.

Intel lancerede Itanium 2 9100-serien med kodenavnet Montvale i november 2007. I maj 2009 blev udgivelsen af Tukwila, Montvales efterfølger, ændret igen, og udgivelsen til OEM'er er planlagt til første kvartal af 2010.

Itanium 9300 (Tukwila): 2010

Itanium 9300-processor-serien med kodenavnet Tukwila blev frigivet den 8. februar 2010 med større ydeevne og hukommelse.

Tukwila anvender en 65 nm-proces, har mellem to og fire kerner, op til 24 MB CPU-cache, Hyper-Threading-teknologi og nye hukommelsescontrollere. Den har også dobbelt datakorrektion af enheder, hvilket hjælper med at løse hukommelsesproblemer. Tukwila har også Intel QuickPath Interconnect (QPI) som erstatning for Itanium-busarkitekturen. Den har en maksimal båndbredde inden for processoren på 96 GB/s og en maksimal hukommelsesbåndbredde på 34 GB/s. Med QuickPath har processoren indbyggede hukommelsescontrollere, som styrer hukommelsen ved hjælp af QPI-grænseflader til kommunikation med andre processorer og I/O-hubs. QuickPath anvendes også med Intel-processorer, der anvender Nehalem-arkitekturen, så Tukwila og Nehalem vil muligvis kunne anvende de samme chipsæt. Tukwila indeholder fire hukommelsescontrollere, som hver især understøtter flere DDR3 DIMM'er via en separat hukommelsescontroller, i lighed med Nehalem Xeon-processoren med kodenavnet Beckton.

Itanium 9500 (Poulson): 2012

| | Denne artikel skal opdateres. Du kan hjælpe Wikipedia ved at opdatere den. (marts 2014) |

Itanium 9500-processoren med kodenavnet Poulson er efterfølgeren til Tukwila og blev frigivet den 8. november 2012. Intel siger, at den springer 45 nm procesteknologien over og bruger 32 nm procesteknologi i stedet; den har 8 kerner, har en 12-wide issue arkitektur, multi-threading tilføjelser og nye instruktioner til parallelisme, herunder virtualisering. Poulson L3-cachestørrelsen er på 32 MB. L2-cachestørrelsen er 6 MB, 512 I KB, 256 D KB pr. kerne. Poulsons størrelse er 544 mm², hvilket er mindre end Tukwila's størrelse (698,75 mm²).

På ISSCC 2011 præsenterede Intel et dokument med titlen "A 32nm 3.1 Billion Transistor 12-Wide-Issue Itanium Processor for Mission Critical Servers". I betragtning af Intels tradition for at dele detaljer om Itanium-mikroprocessorer på ISSCC, henviser dette papir højst sandsynligt til Poulson. Analytiker David Kanter spekulerer i, at Poulson vil anvende en ny arkitektur med en mere avanceret form for multithreading, der anvender op til to tråde, for at forbedre ydeevnen for arbejde med en enkelt tråd og multithreading. De nye oplysninger blev offentliggjort på Hot Chips-konferencen.

De nye oplysninger hævder forbedringer inden for multithreading, forbedringer af pålideligheden (Instruction Replay RAS) og nogle nye instruktioner (trådprioritet, integer-instruktion, cache pre-fetching, dataadgangshinvisninger).

I Intels produktændringsmeddelelse (PCN) 111456-01 var der fire modeller af Itanium 9500-serie CPU'er, som blev fjernet i en revideret version af dokumentet. Delene blev senere opført i Intels database over materialedeklarationsdatablade (MDDS). Intel offentliggjorde senere Itanium 9500-referencemanualen.

Der er tale om følgende modeller:

| Processor nummer | Frekvens |

| 9520 | 1.73 GHz |

| 9540 | 2,13 GHz |

| 9550 | 2,4 GHz |

| 9560 | 2,53 GHz |